# Insider's Guide To The STM32

ARM®Based Microcontroller

An Engineer's Introduction To The STM32 Series

Version 1.8

www.hitex.com

# Published by Hitex (UK) Ltd.

ISBN: 0-9549988 8

First Published February 2008 Second Edition February 2009

#### Hitex (UK) Ltd.

Sir William Lyons Road University Of Warwick Science Park Coventry, CV4 7EZ United Kingdom

#### **Credits**

Author: Trevor Martin

Illustrator: Sarah Latchford

Editors: Michael Beach, Alison Wenlock

Cover: Wolfgang Fuller

# Acknowledgements

The author would like to thank Matt Saunders and David Lamb of ST Microelectronics for their assistance in preparing this book.

# © Hitex (UK) Ltd., 22/10/2009

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical or photocopying, recording or otherwise without the prior written permission of the Publisher.

# **Contents**

| 1.    | Introduction                                       | 4  |

|-------|----------------------------------------------------|----|

| 1.1   | So What Is Cortex?                                 | 4  |

| 1.2   | A Look At The STM32                                | 5  |

| 1.2.1 | Sophistication                                     | 7  |

| 1.2.2 | Safety                                             | 7  |

| 1.2.3 | Security                                           | 7  |

| 1.2.4 | Software Development                               | 7  |

| 1.2.5 | The STM32 Family                                   | 8  |

| 2.    | Cortex Overview                                    | 11 |

| 2.1   | ARM Architectural Revision                         | 11 |

| 2.2   | Cortex Processor And Cortex CPU                    | 12 |

| 2.3   | Cortex CPU                                         | 12 |

| 2.3.1 | Pipeline                                           | 12 |

| 2.3.2 | Programmer's Model                                 | 12 |

| 2.3.3 | CPU Operating Modes                                | 15 |

| 2.3.4 | Thumb-2 Instruction Set                            | 16 |

| 2.3.5 | Memory Map                                         | 17 |

| 2.3.6 | Unaligned Memory Accesses                          | 18 |

| 2.3.7 | Bit Banding                                        | 18 |

| 2.4   | Cortex Processor                                   | 20 |

| 2.4.1 | Busses                                             | 20 |

| 2.4.2 | Bus Matrix                                         | 20 |

| 2.4.3 | System Timer                                       | 21 |

| 2.4.4 | Interrupt Handling                                 | 21 |

| 2.4.5 | Nested Vector Interrupt Controller                 | 22 |

| 2.5   | Power Modes                                        | 28 |

| 2.5.1 | Entering Low Power Mode                            | 28 |

| 2.5.2 | CoreSight Debug Support                            | 28 |

| 2.6   | Cortex Microcontroller Software Interface Standard | 31 |

| 3.    | Getting It Working                                 | 34 |

| 3.1   | Package Types and Footprints                       | 34 |

| 3.2   | Power Supply                                       | 34 |

| 3.3   | Reset Circuit                                      | 35 |

| 3.4   | Oscillators                                        | 36 |

| 3.4.1 | High Speed External Oscillator                     | 36 |

| 3.4.2 | Low Speed External Oscillator                      | 36 |

| 3.4.3 | Clock Output                                       | 36 |

| 3.4.4 | Boot Pins And Field Programming                    | 36 |

| 3.4.5 | Boot Modes                                         | 37 |

| 3.4.6 | Debug Port                                         | 37 |

| 4.    | STM32 System Architecture                          | 39 |

| 4.1   | Memory Layout                                      |    |

| 4.2   | Maximising Performance                             |    |

| 4.2.1 | Phase Locked Loop                                  | 42 |

| 4.2.2 | FLASH Buffer                                       | 43 |

| 4.2.3 | Direct Memory Access                               | 43 |

| 5.    | Peripherals                                        | 49 |

| 11.                | Bibliography                                  | 102 |

|--------------------|-----------------------------------------------|-----|

| 10.                | End Note                                      | 100 |

| 9.1.2<br>9.1.3     | Libraries And Protocol StacksRTOS             |     |

| <b>9.</b><br>9.1.1 | Development Tools  Evaluation Tools           |     |

|                    |                                               |     |

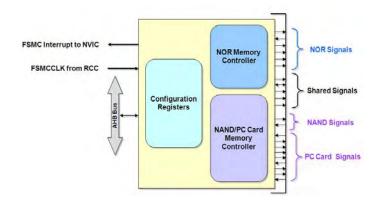

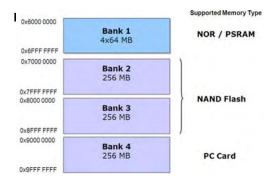

| 8.1.4<br>8.1.5     | Flexible Static Memory Controller             |     |

| 8.1.3              | Option Bytes                                  | 90  |

| 8.1.2              | Erase And Write Operations                    |     |

| 8.1.1              | Internal FLASH Security And Programming       |     |

| 8.1                | The FLASH Module                              |     |

| 8.                 | Memory Regions                                | 89  |

| 7.5.3              | Break Input                                   |     |

| 7.5.2              | Analogue Watchdog                             |     |

| 7.5.1              | GPIO Port Locking                             |     |

| 7.5                | Peripheral Features                           |     |

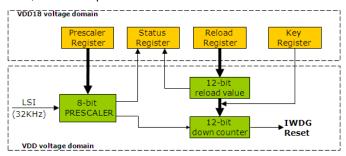

| 7.4.2              | Independent Watchdog                          |     |

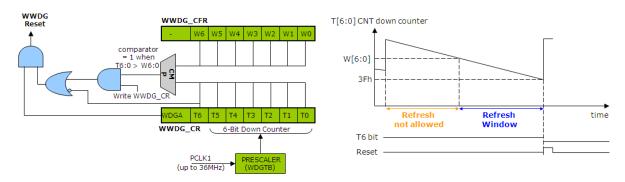

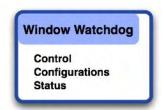

| 7.4.1              | Windowed Watchdog                             |     |

| 7.4                | Watchdogs                                     |     |

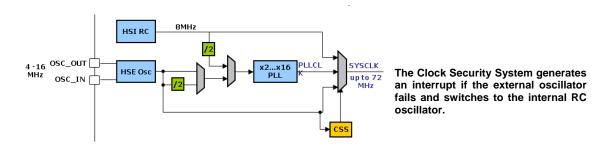

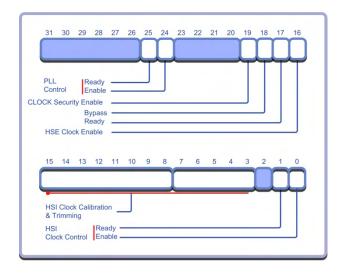

| 7.3                | Clock Security System                         |     |

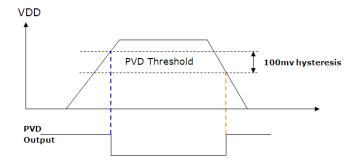

| 7.2                | Power Voltage Detect                          |     |

| 7.<br>7.1          | Reset Control                                 |     |

| 7.                 | Safety Features                               | 83  |

| 6.5                | Debug Support                                 |     |

| 6.4                | Backup Region Power Consumption               |     |

| 6.3                | Standby                                       |     |

| 6.2.2              | STOP Mode                                     |     |

| 6.2.1              | SLEEP                                         |     |

| 6.2                | Low Power Modes                               |     |

| 6.1.1              | Prefetch Buffer And Half-Cycle Mode           |     |

| <b>6.</b> 1        | RUN Mode                                      | _   |

| 6.                 | Low Power Operation                           | 78  |

| 5.4                | USB                                           | 75  |

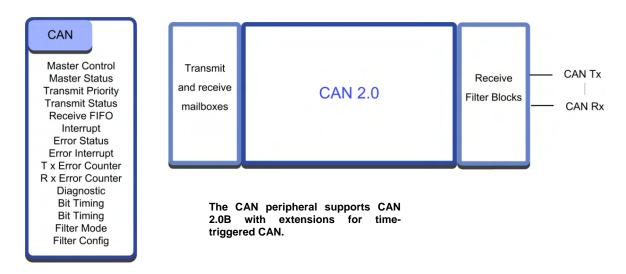

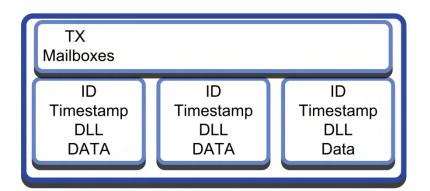

| 5.3.1              | CAN Controller                                |     |

| 5.3                | Can And USB Controller                        |     |

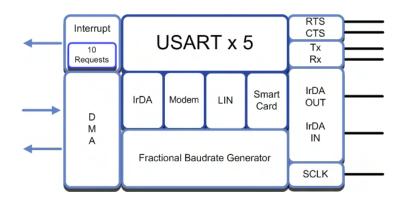

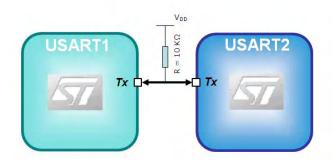

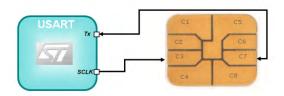

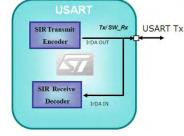

| 5.2.4              | USART                                         |     |

| 5.2.3              | I2C                                           |     |

| 5.2.2              | Inter-Integrated Circuit Sound I2S Peripheral |     |

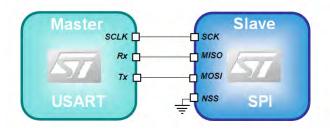

| 5.2.1              | SPI                                           |     |

| 5.2                | Connectivity                                  |     |

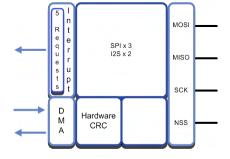

| 5.1.8              | Cyclic Redundancy Check Calculation Unit      |     |

| 5.1.7              | Backup Registers And Tamper Pin               |     |

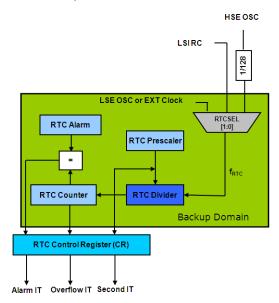

| 5.1.6              | RTC And Backup Registers                      |     |

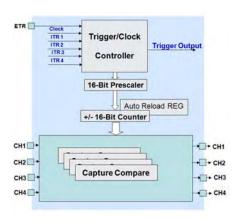

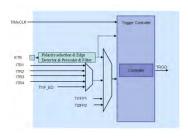

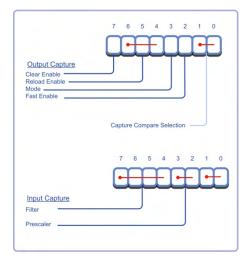

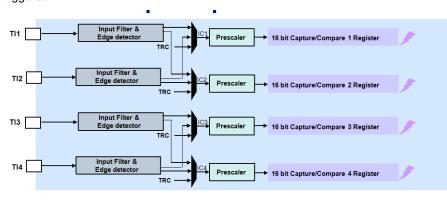

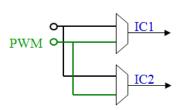

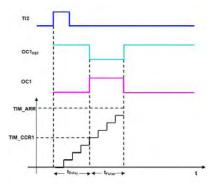

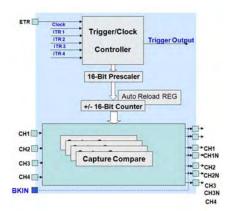

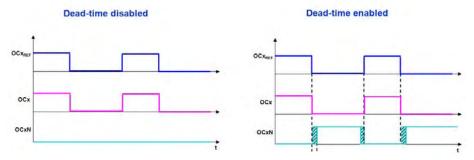

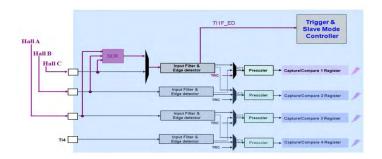

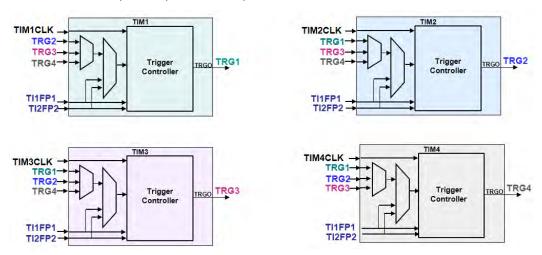

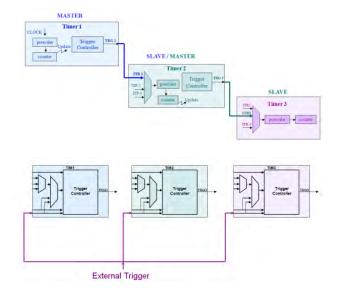

| 5.1.4              | General Purpose And Advanced Timers           |     |

| 5.1.3              | Digital To Analogue Converter                 |     |

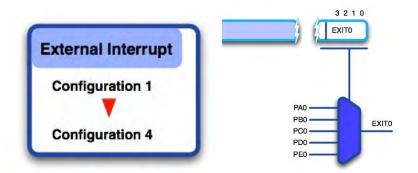

| 5.1.2<br>5.1.3     | External Interrupts ADC                       |     |

| 5.1.1              | General Purpose IO                            |     |

|                    | General Purpose Peripherals                   |     |

# 1. Introduction

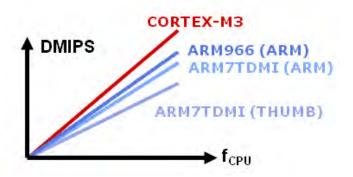

Over the last six or seven years one of the major trends in microcontroller design is the adoption of the ARM7 and ARM9 as *the* CPU for general purpose microcontrollers. Today there are some 240 ARM-based microcontrollers available from a wide range of manufacturers. Now ST Microelectronics have launched the STM32, their first microcontroller based on the new ARM Cortex-M3 microcontroller core. This device sets new standards of performance and cost, as well as being capable of low power operation and hard real-time control.

# 1.1 So What Is Cortex?

The ARM Cortex family is a new generation of processor that provides a standard architecture for a wide range of technological demands. Unlike the other ARM CPUs, the Cortex family is a complete processor core that provides a standard CPU and system architecture. The Cortex family comes in three main profiles: the A profile for high end applications, R for real time and M for cost-sensitive and microcontroller applications. The STM32 is based on the Cortex-M3 profile, which is specifically designed for high system performance combined with low power consumption. It has a low enough cost to challenge traditional 8 and 16-bit microcontrollers.

While the ARM7 and ARM9 CPUs have been successfully integrated into standard microcontrollers, they do show their SoC heritage. This is particularly noticeable in the area of exception and interrupt handling, because each specific manufacturer has designed their own solution. The Cortex-M3 provides a standardised microcontroller core which goes beyond the CPU to provide the entire heart of a microcontroller (including the interrupt system, SysTick timer, debug system and memory map). The 4Gbyte address space of the Cortex-M3 is split into well-defined regions for code, SRAM, peripherals and system peripherals. Unlike the ARM7, the Cortex-M3 is a Harvard architecture and so has multiple busses that allow it to perform operations in parallel, boosting its overall performance. Unlike earlier ARM architectures, the Cortex family allows unaligned data accesses. This ensures the most efficient use of the internal SRAM. The Cortex family also supports setting and clearing of bits within two 1Mbyte regions of memory by a method called bit banding. This allows efficient access to peripheral registers and flags located in SRAM memory without the need for a full Boolean processor.

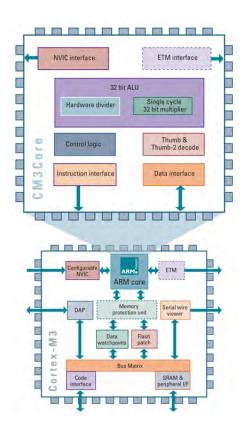

The heart of the STM32 is the Cortex-M3 processor. The Cortex M3 processor is a standardised microcontroller including 32 bit CPU, bus structure, nested interrupt unit, debug system and standard memory layout.

One of the key components of the Cortex-M3 core is the Nested Vector Interrupt Controller (NVIC). The NVIC provides a standard interrupt structure for all Cortex based microcontrollers and exceptional interrupt handling. The NVIC provides dedicated interrupt vectors for up to 240 peripheral sources where each interrupt source can be individually prioritised. The NVIC has been designed for extremely fast interrupt handling. The time taken from receiving an interrupt to reaching the first line of code in your service routine is just twelve cycles. This is achieved in part by automatic stack handling which is done by microcode within the CPU. In the case of back to back interrupts, the NVIC uses a "tail chaining" method that allows successive interrupts to be served with only a six cycle latency. During the interrupt stacking phase, a high priority interrupt can pre-empt a low priority interrupt without incurring any additional CPU cycles. The interrupt structure is also tightly coupled to the low power modes within the Cortex-M3 core. It is possible to configure the CPU to automatically enter a low power on exit from an interrupt. The core then stays asleep until another exception is raised.

Although the Cortex-M3 is designed as a low cost core, it is still a 32-bit CPU and as such has support for two operating modes: Thread mode and Handler mode, which can be configured with their own stacks. This allows more sophisticated software design and support for real-time operating systems. The Cortex core also includes a 24-bit auto reload timer that is intended to provide a periodic interrupt for an RTOS kernel. While the ARM7 and ARM9 CPUs have two instruction sets (the ARM 32-bit and Thumb 16-bit instruction sets) the Cortex family is designed to support the ARM Thumb-2 instruction set. This blends both 16 and 32-bit instructions, to deliver the performance of the ARM 32-bit instruction set with the code density of the Thumb 16-bit instruction set. The Thumb-2 instruction set is a rich instruction set that is designed as a target for C/C++ compilers. This means that a Cortex application can be entirely coded in C.

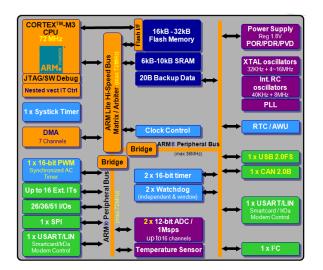

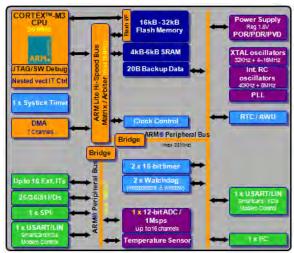

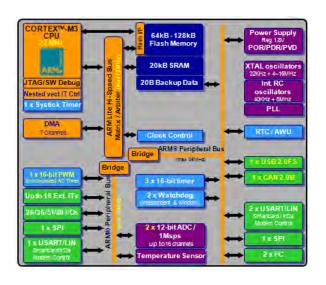

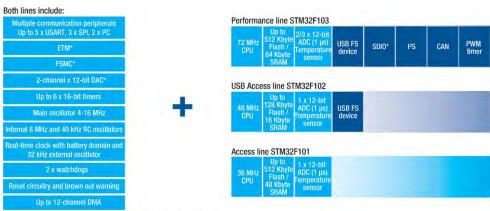

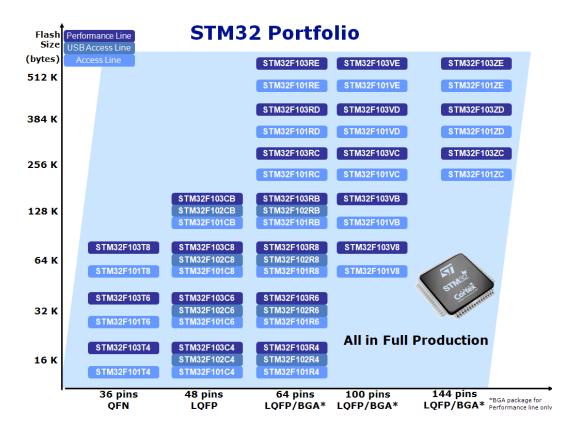

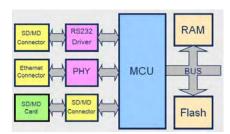

# 1.2 A Look At The STM32

ST already have four ARM7 and ARM9 based microcontroller families, but the STM32 is a significant step up the price/performance curve. With volume pricing at just over one Euro, the STM32 is a serious challenge to existing 16-bit microcontrollers. At the time of writing the STM32 has over 75 different variants with more announced.. These are split into four groups: the performance line which operates up to CPU clock speeds of 72MHz and the access line which runs up to 36MHz, the USB access line which adds a USB device peripheral and runs at CPU clock speeds of 48MHz. A fourth group of variants called the connectivity line has also been announced. The connectivity line adds advanced communication peripherals including Ethernet MAC and a USB Host/OTG controller. All sets of variants are pin and software compatible and offer FLASH ROM sizes up to 512K and 64K SRAM. Since the initial release the STM32 road map has been extended to include devices with larger RAM and FLASH memories and more complex peripherals.

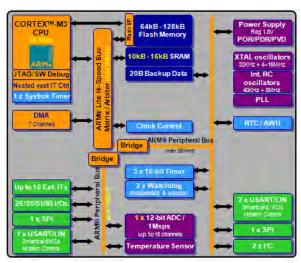

Low Density devices; Performance line and Access line

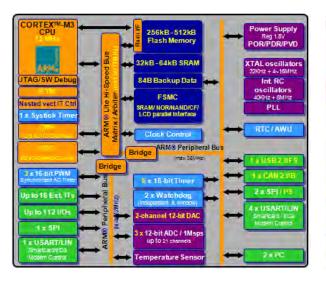

Medium Density devices; Performance line and Access line

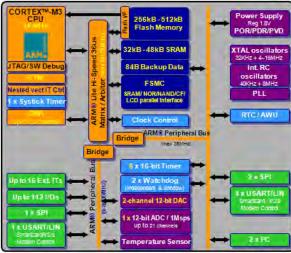

High Density devices ; Performance line and Access line

# 1.2.1 Sophistication

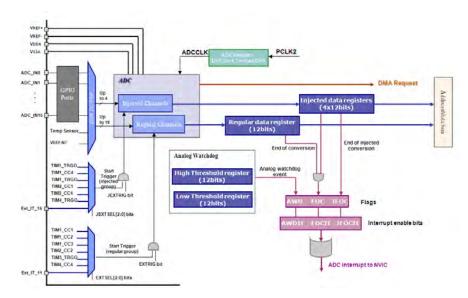

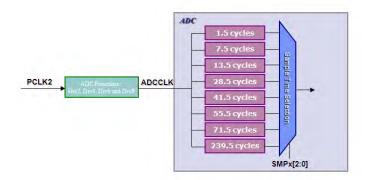

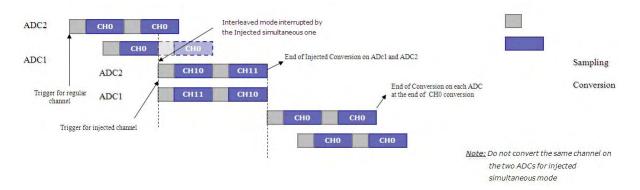

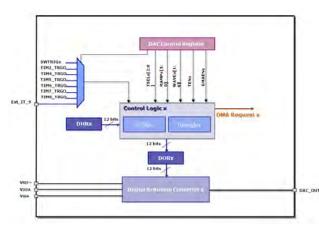

At first glance the peripheral set looks like a typical small microcontroller, featuring peripherals such as Dual ADC, general purpose timers, I2C,SPI,CAN,USB and a real-time clock. However, each of these peripherals is very feature-rich. For example the 12-bit ADC has an integral temperature sensor and multiple conversion modes and devices with dual ADC can slave both ADCs together in a further nine conversion modes. Similarly, each of the four timers has four capture compare units and each timer block may be combined with the others to build sophisticated timer arrays. An advanced timer has additional support for motor control, with 6 complimentary PWM outputs with programmable dead time and a break input line that will force the PWM signal to a pre programmed safe state. The SPI peripheral has a hardware CRC generator for 8 and 16 words to support interfacing to SD and MMC cards.

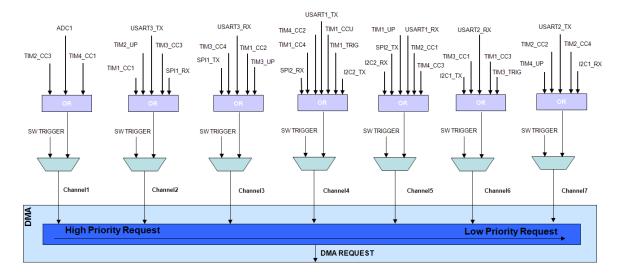

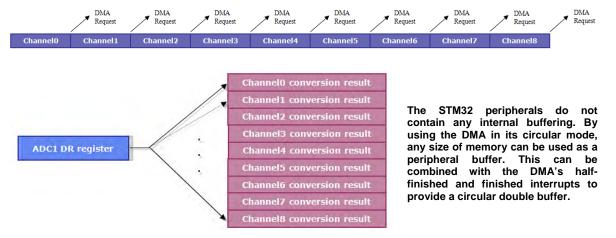

Surprisingly for a small microcontroller, the STM32 also includes a DMA unit with up to 12 channels. Each channel can be used to transfer data to and from any peripheral register on memory location as 8/16 or 32-bit words. Each of the peripherals can be a DMA flow controller sending or demanding data as required. An internal bus arbiter and bus matrix minimise the arbitration between the CPU data accesses and the DMA channels. This means that the DMA unit is flexible, easy to use and really automates data flow within the microcontroller.

In an effort to square the circle the STM32 is a low power as well as high performance microcontroller. It can run from a 2V supply and at 72MHz with everything switched on it consumes just 36mA. In combination with the Cortex low power modes the STM32 has a standby power consumption of just  $2\mu A$ . An internal 8MHz RC oscillator allows the chip to quickly come out of low power modes while the external oscillator is still starting up. This fast entry and exiting from low power modes further reduces overall power consumption.

# 1.2.2 Safety

As well as demanding more processing power and more sophisticated peripherals, many modern applications have to operate in safety-critical environments. With this in mind, the STM32 has a number of hardware features that help support high integrity applications. These include a low power voltage detector, a clock security system and two separate watchdogs. The first watchdog is a windowed watchdog. This watchdog must be refreshed in a defined time frame. If you hit it too soon, or too late, the watchdog will trigger. The second watchdog is an independent watchdog which has its own external oscillator separate from the main system clock. A further clock security system can detect failure of the main external oscillator and fail safely back onto an internal 8MHz RC oscillator.

#### 1.2.3 Security

One of the other unfortunate requirements of modern design is the need for code security to prevent software piracy. Here the STM32 FLASH can be locked for FLASH READ accesses via the debug port. When READ protection is enabled, the FLASH memory is also WRITE protected to prevent untrusted code from being inserted on the interrupt vector table. Further WRITE protection can be enabled over the remainder of the FLASH memory. The STM32 also has a real-time clock and a small area of battery backed SRAM. This region has an anti-tamper input that can trigger an interrupt on a state change. In addition an anti-tamper event will automatically clear the contents of the battery backed SRAM.

# 1.2.4 Software Development

If you are already using an ARM-based microcontroller, the good news is that the chances are that your development tools already support the Thumb-2 instruction set and the Cortex family. The worst case is a software upgrade to get the necessary support. ST also provide a peripheral driver library, a USB developer library as an ANSI C library and source code that is compatible with earlier libraries published for their STR7 and STR9 microcontrollers. Ports of these libraries are already available for popular compiler tools. Similarly, many open source and commercial RTOS and middleware (TCP/IP, file system etc) are available for the Cortex family. The Cortex-M3 also comes with a whole new debug system called CoreSight. Access to the CoreSight system is through the Debug Access Port which supports either a standard JTAG connection or a serial wire (2 Pin) interface. As well as providing debug run control, the CoreSight system on the STM32 provides a data watchpoint

and an instrumentation trace. The instrumentation trace can send selected application information up to the debug tool. This can provide extended debug information and can also be used during software testing.

# 1.2.5 The STM32 Family

The STM32 family has four distinct branches. These are grouped as "Performance Line", "Access Line" and "USB Access Line" devices.ST have also announced a fourth group of variants called the Connectivity line. In the user manual the Performance, USB Access and Access Lines are referred to as the High, Medium and Low density devices. In the Performance, Access and USB Access Lines the peripherals embedded in the devices are richer in the bigger memory devices than on the smaller memory devices. There are therefore three memory ranges and corresponding peripheral sets. The Low density devices have Flash memory sizes from 16KB – 32KB and have the smallest memory set. The Medium density devices have Flash memory sizes from 64KB to 128KB and the High density devices have Flash memory sizes from 256KB to 512KB and have the richest peripheral set.

The Access Line is the entry line for the STM32 family, with 36MHz operation and a simple peripheral set. The Performance Line runs to 72MHz and features more peripherals. The USB Access Line adds a USB device peripheral for cost-sensitive USB applications. ST have also announces a new branch of the STM32 family called the "Connectivity Line". This line brings advanced communications peripherals to the STM32 including a dual role USB controller and an Ethernet MAC. The dual role USB controller can operate as both a device and a Host/OTG controller. The Ethernet MAC also includes IEEE1588 support for real time Ethernet protocols.

Importantly the package types and pins layouts are the same between all the different variants. This allows different versions of the STM32 to be interchanged without having to re-spin the PCB, and with minimal software effort

\*For part numbers starting at 256 Kbytes of embedded Flash

# 2. Cortex Overview

As we saw in the introduction, the Cortex processor is the next generation embedded core from ARM. It is something of a departure from the earlier ARM CPUs in that it is a complete processor core, consisting of the Cortex CPU and a surrounding set of system peripherals, providing the heart of an embedded system. As a result of the wide variety of embedded systems, the Cortex processor is available in a number of application profiles. These are denoted by the letter following the Cortex name. The three profiles are as follows:

Cortex-A Series, applications processors for complex OS and user applications.

Supports the ARM, Thumb and Thumb-2 instruction sets.

Cortex-R Series, real-time systems profile.

Supports the ARM, Thumb, and Thumb-2 instruction sets.

Cortex-M Series, microcontroller profile optimized for cost-sensitive applications.

Supports Thumb-2 instruction set only.

The number at the end of the Cortex name refers to the relative performance level, with 1 the lowest and 8 the highest. Currently performance level 3 is the highest performance level available in the microcontroller profile. The STM32 is based on the Cortex-M3 processor.

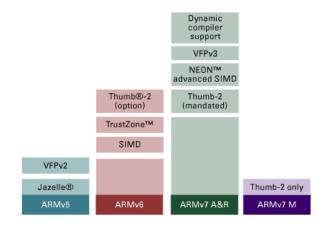

# 2.1 ARM Architectural Revision

ARM also somewhat confusingly denote each of their processors with an architectural revision. (This is written ARMV6, ARMV7 etc.) The Cortex M3 has the architectural revision ARMV7 M.

The Cortex-M3 processor is based on the ARMV7 architecture and is capable of executing the Thumb-2 instruction set.

Thus the documentation for the Cortex-M3 consists of the Cortex-M3 Technical Reference Manual and the ARMV7 M Architectural Reference Manual. Both of these documents can be downloaded from the ARM website at <a href="https://www.arm.com">www.arm.com</a>

## 2.2 Cortex Processor And Cortex CPU

Throughout the remainder of this book, the terms Cortex processor and Cortex CPU will be used to distinguish between the complete Cortex embedded core and the internal RISC CPU. In the next section we will look at the key features of the Cortex CPU followed by the system peripherals in the Cortex processor.

# 2.3 Cortex CPU

At the heart of the Cortex processor is a 32-bit RISC CPU. This CPU has a simplified version of the ARM7/9 programmer's model, but a richer instruction set with good integer maths support, better bit manipulation and 'harder' real-time performance.

# 2.3.1 Pipeline

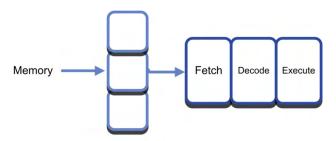

The Cortex CPU can execute most instructions in a single cycle. Like the ARM7 and ARM9 CPUs this is achieved with a three stage pipeline.

Like the ARM7 and ARM9 CPUs the Cortex-M3 has a three stage pipeline. However, the Cortex-M3 also has branch prediction to minimise the number of pipeline flushes.

3 Stage Prefetch

Whilst one instruction is being executed, the next is being decoded and a third is being fetched from memory. This works very well for linear code, but when a branch is encountered the pipeline must be flushed and refilled before code can continue to execute. In the ARM7 and ARM9 CPUs branches are very expensive in terms of code performance. In the Cortex CPU the three stage pipeline is enhanced with branch prediction. This means that when a conditional branch instruction is reached, a speculative fetch is performed, so that both destinations of the conditional instruction are available for execution without incurring a performance hit. The worst case is an indirect branch where a speculative fetch cannot be made and the only course of action is to flush the pipeline. While the pipeline is key to the overall performance of the Cortex CPU, no special considerations need to be made in the application code.

# 2.3.2 Programmer's Model

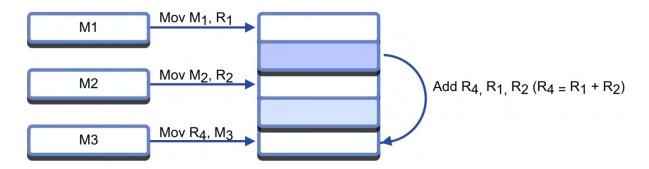

The Cortex CPU is a RISC processor which has a load and store architecture. In order to perform data processing instructions, the operands must be loaded into a central register file, the data operation must be performed on these registers and the results then saved back to the memory store.

The Cortex-M3 is a load and store architecture. All data has to be moved into a central register file before a data processing instruction can act on it.

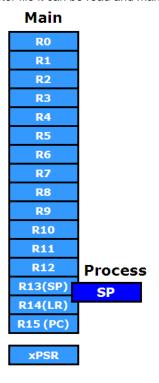

Consequently all the program activity focuses around the CPU register file. This register file consists of sixteen 32-bit wide registers. Registers R0-R12 are simple registers that can be used to hold program variables. The Registers R13-R15 have special functions within the Cortex CPU. Register R13 is used as the stack pointer. This register is banked, which allows the Cortex CPU to have two operating modes each with their own separate stack space. This is typically used by an RTOS which can run its 'system' code in a protected mode. In the Cortex CPU the two stacks are called the main stack and the process stack. The next register R14 is called the link register. This register is used to store the return address when a call is made to a procedure. This allows the Cortex CPU to make a fast entry and exit to a procedure. If your code calls several levels of subroutines, the compiler will automatically store R14 on the stack. The final register R15 is the program counter; since this is part of the central register file it can be read and manipulated like any other register.

The Cortex-M3 has a CPU register file of 16 32-bit wide registers. Like the earlier ARM7/9 CPUs R13 is the stack pointer. R14 is the link register and R15 is the PC. R13 is a banked register to allow the Cortex-M3 to operate with two stacks: a process stack and a main stack.

#### 2.3.2.1 XPSR

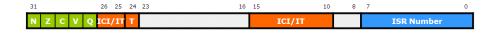

In addition to the register file there is a separate register called the Program Status Register. This is not part of the main register file and is only accessible through two dedicated instructions. The xPSR contains a number of fields that influence the execution of the Cortex CPU.

The Program Status Register contains status fields for instruction execution. This register is aliased into the Application, Execution and Interrupt Status Registers

The xPSR register can also be accessed through three special alias names that allow access to sub-ranges of bits within the xPSR. The top five bits are the condition code flags and are aliased as the Application Program Status Register. The first four condition code flags N,Z,C,V (Negative, Zero, Carry and Overflow) will be set and cleared depending on the result of a data processing instruction. The Q bit is used by the DPS saturated maths instructions to indicate that a variable has reached its maximum or minimum value. Like the ARM 32-bit instruction set, certain Thumb-2 instructions are only executed if the instruction condition code matches the state of the Application Program Status Register flags. If the instructions condition codes do not match, the instruction passes through the pipeline as a NOP. This ensures that instructions flow smoothly through the pipeline and minimises pipeline flushes. In the Cortex CPU, this technique is extended with the Execution Program Status

Register. This is an alias of bits 26 – 8 of the xPSR. This contains three fields: the "If then" field the "interrupt continuable instruction" and the Thumb instruction field. The Thumb-2 instruction set has an efficient method of executing small 'if then' blocks of instructions. When a conditional test is true, it can set a value in the IT field that tells the CPU to execute up to four following instructions. If the conditional test fails, these instructions will pass through the pipeline as a NOP. Thus a typical line of C would be coded as follows:

While most Thumb-2 instructions execute in a single cycle, some (such as load and store instructions) take multiple cycles. So that the Cortex CPU can have a deterministic interrupt response time, these instructions must be interruptible. When an instruction is terminated early, the interrupt continuable instruction field stores the number of the next register to be operated on in the load or store multiple instruction. Thus once the interrupt has been serviced, the load/store multiple instruction can resume execution. The final Thumb field is inherited from the earlier ARM CPUs. This field indicates if the ARM or Thumb instruction set is currently being executed by the CPU. In the Cortex-M3 this bit is always set to one. Finally, the interrupt status field contains information on any interrupt request that was pre-empted.

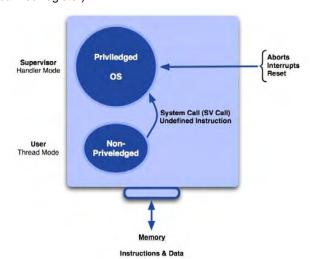

# 2.3.3 CPU Operating Modes

While the Cortex processor is designed to be a low gate count, fast and easy to use microcontroller core, it has been designed to support the use of a real-time operating system. The Cortex processor has two operating modes: Thread mode and Handler mode. The CPU will run in Thread mode while it is executing in non-interrupt background mode and will switch to the Handler mode when it is executing exceptions. In addition, the Cortex CPU can execute code in a privileged or non-privileged mode. In privileged mode, the CPU has access to the full instruction set. In unprivileged mode certain instructions are disabled (such as the MRS and MSR instructions which allow access to the xPSR and its aliases). Additionally, access to most registers in the Cortex processor system control space is also disabled. Stack usage can also be configured. The main stack (R13) can be used by both Thread and Handler mode. Alternatively, Handler mode can be configured to use the process stack (R13 banked register).

The Cortex-M3 can be used in a 'flat' simple mode. It is also designed to support real-time operating systems. It has Handler and Thread modes that can be configured to use the main and process stacks and have privileged access to the Cortex system control registers.

|                        |                                                                     | Operations<br>(privilege out of reset) | Stacks<br>(Main out of reset)           |

|------------------------|---------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| <b>es</b><br>of reset) | Handler - An exception is being processed                           | Privileged execution<br>Full control   | Main Stack Used by<br>OS and Exceptions |

| Mode<br>(Thread out    | Thread - No exception is being processed - Normal code is executing | Privileged/Unprivileged                | Main/Process                            |

Out of reset the Cortex processor will run in a 'flat' configuration. Both Thread and Handler modes execute in privileged mode, so there are no restrictions on access to any processor resources. Both the Thread and Handler modes use the main stack. In order to start execution, the Cortex processor simply needs the reset vector and the start address of the stack to be configured before you can start to execute your application C code. However, if you are using an RTOS or are developing a safety-critical application, the chip can be used in a mode advanced configuration where Handler mode (exceptions and the RTOS) runs in privileged mode and uses the main stack while application code runs in Thread mode with unprivileged access and uses the process stack. This way the system code and the application code are partitioned and errors in the application code will not cause the RTOS to crash.

#### 2.3.4 Thumb-2 Instruction Set

The ARM7 and ARM9 CPUs can execute two instruction sets: the ARM 32-bit instruction set and the Thumb 16-bit instruction set. This allows a developer to optimise his program by selecting the instruction set used for different procedures: 32-bit instructions for speed and 16-bit instructions for code compression. The Cortex CPU is designed to execute the Thumb-2 instruction set which is a blend of 16 and 32 bit instructions. The thumb-2 instruction set gives a 26% code density improvement over the ARM 32-bit instruction set and a 25% improvement in performance over the Thumb 16-bit instruction set. The Thumb2 instruction set has some improved multiply instructions which can execute in a single cycle and a hardware divide that takes between 2-7 cycles.

The Cortex processor benchmarks give a performance level of 1.2 DMIPS/MHz, which is 1.2 Clock cycles per instruction.

| Source    | Destination | Cycles |

|-----------|-------------|--------|

| 16b x 16b | 32b         | 1      |

| 32b x 16b | 32b         | 1      |

| 32b x 32b | 32b         | 1      |

| 32b x 32b | 64b         | 3-7*   |

The Thumb-2 instruction set also has: improved branching instructions including test and compare, if/then conditional execution blocks and for data manipulation byte ordering and byte and half word extraction instructions. While still a RISC processor, the Cortex CPU also has a rich instruction set that is specifically designed as a good target for a C compiler. A typical Cortex-M3 program will be written entirely in ANSI C, with minimal non-ANSI keywords and only the exception vector table written in Assembler.

# 2.3.5 Memory Map

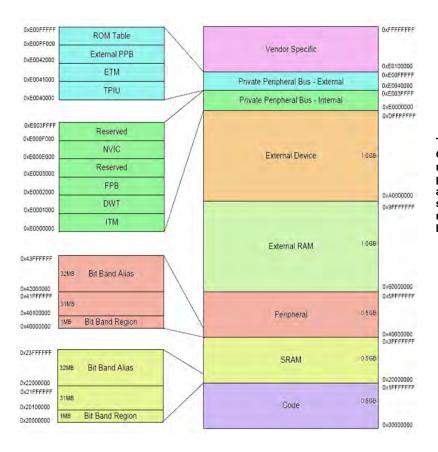

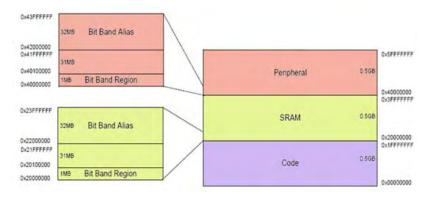

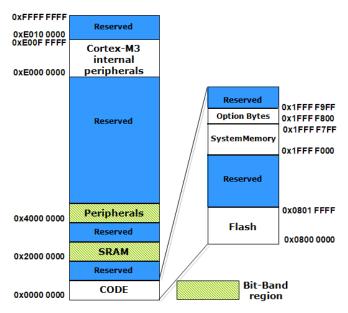

The Cortex-M3 processor is a standardised microcontroller core and as such has a well-defined memory map. Despite the multiple internal busses this memory map is a linear 4 Gbyte address space.

The Cortex-M3 defines a fixed 4 Gb memory map that specifies regions for code SRAM peripherals, external memory and devices and the Cortex system registers. This memory map is common to all Cortex-based devices.

The first 1Gbyte of memory is split evenly between a code region and a SRAM region. The code space is optimised to be executed from the I-Code bus. Similarly, the SRAM is reached with the D-code bus. Although code can be loaded and executed from the SRAM, the instructions would be fetched using the system bus, which incurs an extra wait state. It is likely that code would run slower from SRAM than from on-chip FLASH memory located in the code region. The next 0.5 Gbyte of memory is the on-chip peripheral region. All user peripherals provided by the microcontroller vendor will be located in this region. The first 1 Mbyte of both the SRAM and Peripheral regions is bit-addressable using a technique called bit banding. Since all the SRAM and all the user peripherals on the STM32 are located in these regions all the memory locations of the STM32 can be manipulated in a word-wide or bitwise fashion. The next 2 Gbyte address space is allocated to external memory-mapped SRAM and peripherals. The final 0.5 Gbyte is allocated to the internal Cortex processor peripherals and a region for future vendor specific enhancements to the Cortex processor. All of the Cortex processor registers are at fixed locations for all Cortex-based microcontrollers. This allows code to be more easily ported between different STM32 variants and indeed other vendors' Cortex-based microcontrollers. One processor to learn, one set of tools to invest in and large amounts of reusable code across a wide range of microcontrollers.

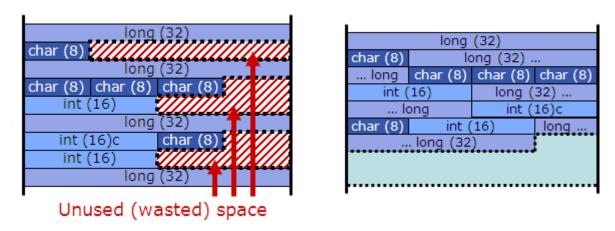

# 2.3.6 Unaligned Memory Accesses

The ARM7 and ARM9 instruction sets are capable of accessing byte, half word and word signed and unsigned variables. This allows the CPU to naturally support integer variables without the need for the sort of software library support typically required in 8 and 16-bit microcontrollers. However, the earlier ARM CPUs do suffer from a disadvantage in that they can only do word or half-word aligned accesses. This restricts the compiler linker in its ability to pack data into the SRAM and some valuable SRAM will be wasted. (This can be as much as 25% depending on the mix of variables used.)

The Cortex-M3 can make unaligned memory accesses, which ensures that the SRAM is efficiently used.

The Cortex CPU has addressing modes for word, half-word and byte, but is able to make unaligned memory accesses. This gives the compiler linker complete freedom to order the program data in memory. The additional bit banding support on the Cortex CPU allows program flags to be packed into a word or half-word variable rather than using a byte for each flag.

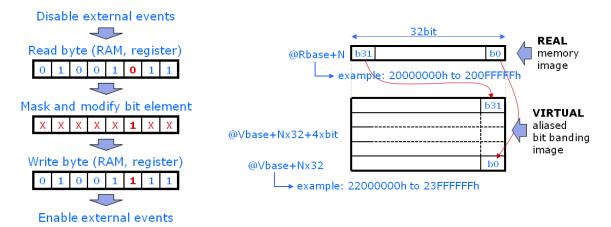

#### 2.3.7 Bit Banding

The earlier ARM7 and ARM9 CPUs were only able to perform bit manipulations on SRAM and peripheral memory locations by using AND and OR operations. This requires a READ MODIFY WRITE operation which is expensive in terms of the number of cycles taken to set and clear individual bits and the overall code space required for each bit manipulation.

The bit banding technique allows atomic bit manipulation while keeping the Cortex-M3 CPU to a minimal gate count.

To overcome this limitation it would be possible to introduce a dedicated bit set and clear instructions, or a full Boolean processor, but this would increase the size and complexity of the Cortex CPU. Instead, a technique called bit banding allows direct bit manipulation on sections of the peripheral and SRAM memory spaces, without the need for any special instructions. The bit addressable regions of the Cortex memory map are composed of the bit band region (which is up to 1Mbyte of real memory or peripheral registers) and the bit band Alias region which takes up to 32Mbyte of the memory map. Bit banding works by mapping each bit in the bit band region to a word address in the Alias region. So by setting and clearing the aliased word address we can set and clear bits in the real memory.

Bit Banding is supported over the first 1Mb of the SRAM and Peripheral regions. This covers all the resources of the STM32.

This allows us to perform individual bit manipulation without the need for special instructions and keeps the overall size of the Cortex core as small as possible. In practice, we need to calculate the address of the bit band alias word for a given memory location in the peripheral or SRAM space. The formula to calculate the alias address is as follows:

Address in the bit band alias region = Bit band alias base address + bit word offset

Where bit word offset = Byte offset from bit band base X 0x20 + bit number x 4

This is much easier than it may look at first glance. For a practical example, the GPIO output data register is written to in order to set and clear individual IO lines. The physical address of the Port B output register is 0x40010C0C. In this example we want to be able to set and clear bit eight of this word using the above formula.

Word address= 0x40010C0CPeripheral bit band base= 0x40000000Peripheral bit band Alias base= 0x42000000

Byte offset from bit band base = 0x40010C0C - 0x40000000 = 10C0CBit word offset  $= (0x10C0C \times 0x20) + (8x4) = 0x2181A0$ Bit Alias address = 0x42000000 + 0x2181A0 = 0x422181A0

We can now create a pointer to this address using the following line of C:

```

#define PortBbit8 (*((volatile unsigned long *) 0x422181A0 ))

```

This pointer can then be used to set and clear the IO port bit:

```

PB8 = 1; //led on

```

Which generates the following assembly instructions:

MOVS r0,#0x01 LDR r1,[pc,#104] STR r0,[r1,#0x00]

Switching the LED off:

```

PB8 = 0; //led off

```

Generates the following assembly instructions:

```

MOVS r0,#0x00

LDR r1,[pc,#88]

STR r0,[r1,#0x00]

```

Both the set and clear operations take three 16-bit instructions and on the STM32 running at 72 MHz these instructions are executed in 80nsec. Any word in the peripheral and SRAM bit band regions can also be directly addressed word-wide so we could perform the same set and clear using the more traditional AND and OR approach:

```

GPIOB->ODR | = 0x00000100;

//LED on

LDR

r0,[pc,#68]

ADDS

r0, r0, #0x08

LDR

r0, [r0, #0x00]

ORR

r0, r0, #0x100

r1, [pc, #64]

LDR

STR

r0,[r1,#0xC0C]

GPIOB->ODR &=!0x00000100;

//LED off

r0, [pc, #40]

LDR

ADDS

r0, r0, #0x08

LDR

r0, [r0, #0x00]

r0,#0x00

MOVS

r1,[pc,#40]

LDR

r0, [r1, #0xC0C]

STR

```

Now each set and clear operation takes a mixture of 16 and 32-bit operations, which take a minimum of 14 bytes for each operation and at the same clock frequency take a minimum of 180 nSec. If you consider the impact of bit banding on a typical embedded application that sets and clears lots of bits in the peripheral registers and uses semaphores and flags in the SRAM, you are very clearly going to make significant savings in both code size and execution time and it is all handled in the STM32 header file for you.

# 2.4 Cortex Processor

#### 2.4.1 Busses

The Cortex-M3 processor has a Harvard architecture with separate code and data busses. These are called the lcode bus and the Dcode bus. Both of these busses can access code and data in the range 0x00000000 – 0x1FFFFFFF. An additional system bus is used to access the Cortex system control space in the range 0x20000000-0xDFFFFFFF and 0xE0100000-0xFFFFFFF. The Cortex on-chip debug system has an additional bus structure called the Private Peripheral Bus.

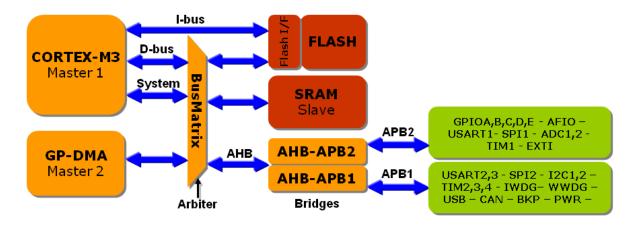

# 2.4.2 Bus Matrix

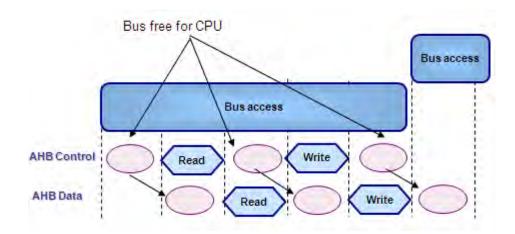

The system and data busses are connected to the external microcontroller via a set of high speed busses arranged as a bus matrix. This allows a number of parallel paths between the Cortex busses and other external bus masters such as DMA to the on-chip resources such as SRAM and peripherals. If two bus masters (i.e. the Cortex CPU and a DMA channel) try to access the same peripheral, an internal arbiter will resolve the conflict and grant bus access to the highest priority peripheral. However, in the STM32 the DMA units are designed to work in concert with the Cortex CPU, as we will see when we examine the operation of the DMA unit.

# 2.4.3 System Timer

The Cortex core also includes a 24-bit down counter, with auto reload and end of count interrupt. This is intended to provide a standard timer for all Cortex-based microcontrollers. The SysTick timer is intended to be used to provide a system tick for an RTOS, or to generate a periodic interrupt for scheduled tasks. The SysTick Control and status register in the Cortex-M3 System control space unit allows you to select the SysTick clock source. By setting the CLKSOURCE bit the SysTick timer will run at the CPU frequency. When cleared the timer will run at 1/8 CPU frequency.

The SysTick Timer is a 24-bit auto-reload timer located within the Cortex-M3 processor. It is intended to provide a timer tick for a Real Time Operating System.

The SysTick timer has three registers. The current value and reload value should be initialised with the count period. The control and status register contains an ENABLE bit to start the timer running and a TICKINT bit to enable its interrupt line. In the next section we will look at the Cortex interrupt structure and use the SysTick timer to generate a first exception on the STM32.

#### 2.4.4 Interrupt Handling

One of the key improvements of the Cortex core over the earlier ARM CPUs is its interrupt structure and exception handling. The ARM7 and ARM9 CPUs had two interrupt lines: the fast interrupt and the general purpose interrupt line. These two interrupt lines had to support all of the interrupt sources within a given manufacturer's microcontroller. How this was done varied according to the implementation, so while the techniques used were broadly the same, the implementation differed between manufacturers. The ARM7 and ARM9 interrupt structure suffers from two further problems. Firstly it is not deterministic; the time taken to terminate or abort an instruction under execution when the interrupt occurs is variable. This may not be a problem for many applications, but it is a big issue in real-time control. Secondly, the ARM7 and ARM9 interrupt structure does not naturally support nested interrupts; further software is required: either Assembler macros or an RTOS. One of the key criteria of the Cortex core is to overcome these limitations and provide a standard interrupt structure which is both extremely fast and deterministic.

# 2.4.5 Nested Vector Interrupt Controller

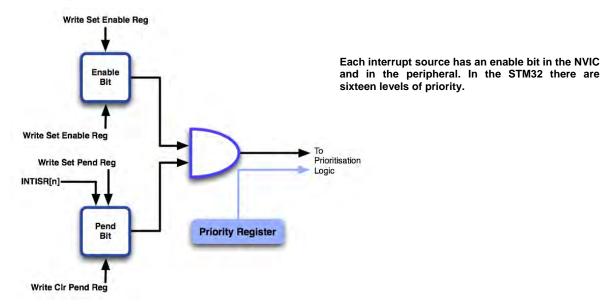

The Nested Vector Interrupt Controller is a standard unit within the Cortex core. This means that all Cortex-based microcontrollers will have the same interrupt structure, regardless of manufacturer. Thus application code and operating systems can be easily ported from one microcontroller to another and the programmer does not need to learn a whole new set of registers. The NVIC is also designed to have a very low interrupt latency. This is both a feature of the NVIC itself and of the Thumb-2 instruction set which allows multi-cycle instructions such as load and store multiple to be interruptible. This interrupt latency is also deterministic, with several advanced interrupt handling features that support real-time applications. As its name implies, the NVIC is designed to support nested interrupts and on the STM32 there are 16 levels of priority. The NVIC interrupt structure is designed to be programmed entirely in 'C' and does not need any Assembler macros or special non-ANSI directives.

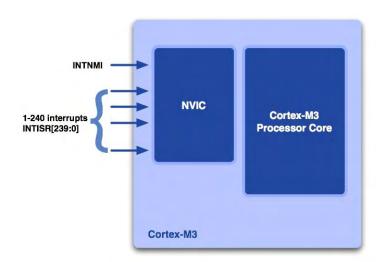

The STM32 processor includes a Nested Vector Interrupt Controller which can support a maximum of 240 external peripherals.

Although the NVIC is a standard unit within the Cortex core, in order to keep the gate count to a minimum the number of interrupt lines going into the NVIC is configurable when the microcontroller is designed. The NVIC has one non-maskable interrupt and up to a further 240 external interrupt lines which can be connected to the user peripherals. There are an additional 15 interrupt sources within the Cortex core, which are used to handle internal exceptions within the Cortex core itself. The STM32 NVIC has been synthesised with a maximum of 43 maskable interrupt lines.

# 2.4.5.1 NVIC Operation Exception Entry And Exit

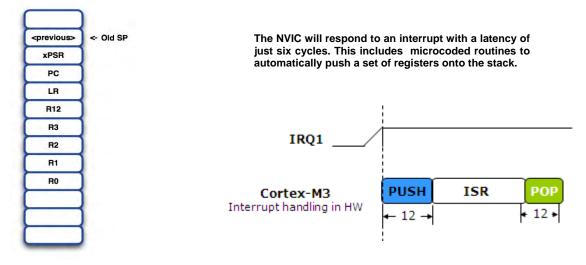

When an interrupt is raised by a peripheral, the NVIC will start the Cortex CPU serving the interrupt. As the Cortex CPU enters its interrupt mode, it will push a set of registers onto the stack. Importantly this is done in microcode, so there is no instruction overhead in the application code. While the stack frame is being saved, the starting address of the interrupt service routine is fetched on the instruction bus. Thus the time taken from the interrupt being raised to reaching the first instruction in the interrupt routine is just 12 cycles.

The stack frame consists of the Program Status Register, the program counter and the link register. This saves the context that the Cortex CPU was running in. In addition registers R0 – R3 are also saved. In the ARM binary interface standard these registers are used for parameter passing, so saving these gives us a set of CPU registers that can be used by the ISR. Finally R12 is also saved; this register is the intracall scratch register. This register is used by any code that runs when function calls are made. For example, if you have enabled stack checking in the compiler, the additional code generated will use R12 if it need a CPU register. When the interrupt ends the process is reversed, the stack frame is restored automatically by microcode and in parallel the return address is fetched, so that the background code can resume execution in 12 cycles.

# 2.4.5.2 Advanced Interrupt Handling Modes

As well as being able to handle a single interrupt very quickly, the NVIC is designed to efficiently handle multiple interrupts in a very real time application. The NVIC has several clever methods of handling multiple interrupt sources the minimum delay between interrupts and to ensure that the highest priority interrupt is served first.

# 2.4.5.2.1 Interrupt Pre-emption

The NVIC is also designed to allow high priority interrupts to pre-empt a currently running low priority interrupt. In this case the running interrupt is halted and a new stack frame is saved in the standard 12 cycles after which the high priority interrupt runs. When the high priority interrupt is finished, the stack is automatically POPed and the low priority interrupt can resume execution.

# 2.4.5.2.2 Tail Chaining

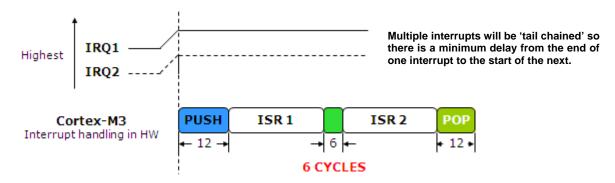

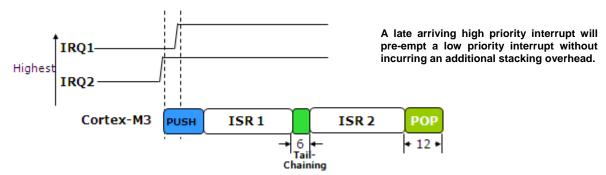

If a high priority interrupt is running and a low priority interrupt is raised, the Cortex NVIC uses a method called tail chaining to ensure that there is a minimum delay between servicing interrupts.

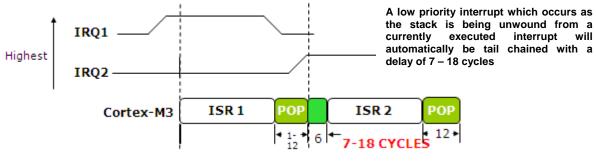

If two interrupts are raised, the highest priority interrupt will be served first and will begin execution in the standard 12 cycles. However, at the end of the interrupt routine the Cortex CPU does not return to the background code. The stack frame is not restored, only the entry address of the next highest priority ISR is fetched. This takes just six cycles and then the next interrupt service routine can begin execution. At the end of the pending interrupts the stack is restored and the return address is fetched, so the background code can begin execution in the standard 12 cycles. If the low priority interrupt arrives while the running interrupt is exiting, the POP will be abandoned and the stack pointer will be wound back to its original value. There is an additional 6 cycle delay while the new ISR address is fetched. This gives a latency of between 7 – 18 cycles before the new interrupt service routine can begin execution.

#### 2.4.5.2.3 Late Arrival

In a real-time system there may often be a condition where we have started to serve a low priority interrupt, only for a high priority interrupt to be raised. If this condition occurs during the initial PUSH the NVIC will switch to serve the higher priority interrupt. The stacking continues and there will be a minimum of 6 cycles from the point at which the high priority interrupt is raised, while the new ISR address is fetched.

Once the high priority interrupt has finished execution, the original low priority interrupt will be tail chained and begin execution six cycles later.

# 2.4.5.3 NVIC Configuration And Use

To use the NVIC we need to do three things. First configure the vector table for the interrupt sources we want to use. Next configure the NVIC registers to enable and set the priorities of the NVIC interrupts and lastly we must configure the peripheral and enable its interrupt support.

# 2.4.5.3.1 Exception Vector Table

The Cortex vector table starts at the bottom of the address range. However rather than start at zero the vector table starts at address 0x00000004 the first four bytes are used to store the starting address of the stack pointer.

| No.  | Exception Type  | Priority     | Type of<br>Priority | Descriptions                                  |

|------|-----------------|--------------|---------------------|-----------------------------------------------|

| 1    | Reset           | -3 (Highest) | fixed               | Reset                                         |

| 2    | NMI             | -2           | fixed               | Non-Maskable Interrupt                        |

| 3    | Hard Fault      | -1           | fixed               | Default fault if other hander not implemented |

| 4    | MemManage Fault | 0            | settable            | MPU violation or access to illegal locations  |

| 5    | Bus Fault       | 1            | settable            | Fault if AHB interface receives error         |

| 6    | Usage Fault     | 2            | settable            | Exceptions due to program errors              |

| 7-10 | Reserved        | N.A.         | N.A.                |                                               |

| 11   | SVCall          | 3            | settable            | System Service call                           |

| 12   | Debug Monitor   | 4            | settable            | Break points, watch points, external debug    |

| 13   | Reserved        | N.A.         | N.A.                |                                               |

| 14   | PendSV          | 5            | settable            | Pendable request for System Device            |

| 15   | SYSTICK         | 6            | settable            | System Tick Timer                             |

| 16   | Interrupt #0    | 7            | settable            | External Interrupt #0                         |

|      |                 |              | settable            |                                               |

| 256  | Interrupt#240   | 247          | settable            | External Interrupt #240                       |

The Cortex exception table contains the start address or an ISR which is loaded into the Program counter as the CPU enters the exception.

Each of the interrupt vector entries is four bytes wide and holds the start address of each service routine associated with the interrupt. The first 15 entries are for exceptions that occur within the Cortex core. These include the reset vector, non-maskable interrupt, fault and error management, debug exceptions and also the SysTick timer interrupt. The Thumb-2 instruction set also includes system service call instruction which when executed will generate an exception. The user peripheral interrupts start from entry 16 and will be linked to peripherals as defined by the manufacturer. In software, the vector table is usually maintained in the startup by locating the service routine addresses at the base of memory.

```

RESET, DATA, READONLY

AREA

___Vectors

EXPORT

Vectors

DCD

initial_sp

; Top of Stack

; Reset Handler

DCD

Reset Handler

DCD

NMI Handler

; NMI Handler

; Hard Fault Handler

DCD

HardFault Handler

DCD

MemManage_Handler

; MPU Fault Handler

DCD

BusFault_Handler

Bus Fault Handler

DCD

UsageFault_Handler

; Usage Fault Handler

DCD

; Reserved

DCD

0

; Reserved

; Reserved

DCD

0

DCD

0

; Reserved

; SVCall Handler

DCD

SVC Handler

DCD

DebugMon Handler

; Debug Monitor Handler

DCD

; Reserved

; PendSV Handler

PendSV Handler

DCD

DCD

SysTick_Handler

; SysTick Handler

```

In the case of the SysTick timer we can create a service routine by declaring a 'C' routine with the matching symbolic name:

```

void SysTick_Handler (void)

{

....

}

```

Now with the vector table configured and the ISR prototype defined, we can configure the NVIC to handle the SysTick timer interrupt. Generally we need to do two things: set the priority of the interrupt and then enable the interrupt source. The NVIC registers are located in the system control space.

# Interrupt Control IRQ SET and CLEAR IRQ Pending IRQ ACTIVE IRQ PRIORITY System Control System Priority

**Fault Status**

The NVIC registers are located in the Cortex-M3 System control space and may only be accessed when the CPU is running in privileged mode.

The Cortex internal exceptions are configured using the system control and system priority registers, while the user peripherals are configured using the IRQ registers. The SysTick interrupt is an internal Cortex exception and is handled in the system registers. Some of the internal exceptions are permanently enabled; these include the reset and NMI interrupts, but also the SysTick timer, so there is no explicit action required to enable the SysTick interrupt within the NVIC. To configure the SysTick interrupt we need to set the timer going and enable the interrupt within the peripheral itself:

```

SysTickCurrent = 0x9000;  //Start value for the sys Tick counter

SysTickReload = 0x9000;  //Reload value

SysTickControl = 0x07;  //Start and enable interrupt

```

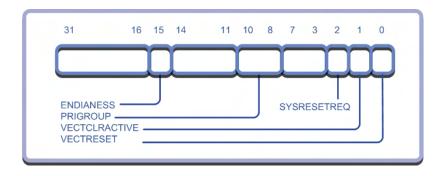

The priority of each of the internal Cortex exceptions can be set in the system priority registers. The Reset, NMI and hard fault exceptions are fixed to ensure that the core will always fallback to a known exception. Each of the other exceptions has an eight bit field located in the three system priority registers. The STM32 only implements 16 levels of priority so only four bits of this field are active. However it is important to note that the priority is set by the four most significant bits.

Each of the USER peripherals is controlled by the IRQ register blocks. Each user peripheral has an Interrupt Enable bit. These bits are located across two 32-bit IRQ Set Enable registers. There are matching IRQ Clear Enable registers that are used to disable an interrupt source. The NVIC also includes pending and active registers that allow you to determine the current condition of an interrupt source.

There are sixteen priority registers. Each priority register is divided into four eight bit priority fields, each field being assigned to an individual interrupt vector. The STM32 only uses half of this field to implement 16 levels of priority. However, you should note that the active priority bits are in the upper nibble of each priority field. By default the priority field defines 16 levels of priority with level zero the highest and 15 the lowest. It is also possible to format the priority field into priority groups and subgroups. This does not provide extra levels of priority, but helps management of priority levels when you have a large number of interrupts by programming the PRIGROUP field in the Application Interrupt and Reset Control Register.

The PRIGROUP field splits the priority levels into groups and subgroups. This is useful for software abstraction when dealing with a large number of interrupts.

| PRIGROUP<br>(3 Bits) | Binary Point<br>(group.sub) |         | Preempting Priority<br>(Group Priority) |        | Sub-Priority |        |

|----------------------|-----------------------------|---------|-----------------------------------------|--------|--------------|--------|

| (3 bits)             | (gro                        | ip.aut/ | Bits                                    | Levels | Bits         | Levels |

| 011                  | 4.0                         | 9999    | 4                                       | 16     | 0            | 0      |

| 100                  | 3.1                         | gggs    | 3                                       | 8      | 1            | 2      |

| 101                  | 2.2                         | ggss    | 2                                       | 4      | 2            | 4      |

| 110                  | 1.3                         | gs55    | 1                                       | 2      | 3            | 8      |

| 111                  | 0.4                         | 5555    | 0                                       | 0      | 4            | 16     |

The three bit PRIGROUP field allows you to split the 4-bit priority fields into groups and subgroups. For example, PRIGROUP value 3 creates two groups, each with four levels of priority. In your application code you can now define a high priority group of interrupts and a low priority group. Within each group you can specify subgroup levels of low, medium, high and very high. As mentioned above this does not provide you anything "extra" but provides a more abstracted view of the interrupt structure which is useful to the programmer when managing a large number of interrupts. Configuring a peripheral interrupt is very similar to configuring an internal Cortex exception. In the case of the ADC interrupt we must first set the interrupt vector and provide the ISR routine:

```

DCD ADC_IRQHandler

void ADC_Handler void

{

}

```

Then the ADC must be initialised and the interrupt must be enabled within the peripheral and the NVIC:

```

ADC1->CR2

= ADC CR2;

//Switch on the ADC and continuous conversion

= sequence1; //Select number of channels in sequence conversion

ADC1->SQR1

ADC1->SQR2

= sequence2; //and select channels to convert

ADC1->SQR3

= sequence3;

ADC1->CR2

= ADC CR2;

//Rewrite on bit

ADC1->CR1

= ADC_CR1;

//Start regular channel group, enable ADC interrupt

= 0x33333333; //Set LED pins to output

GPIOB->CRH

NVIC->Enable[0] = 0x00040000; //Enable ADC interrupt

NVIC \rightarrow Enable[1] = 0x000000000;

```

# 2.5 Power Modes

We will have a look at the full power management options within the STM32 later. In this section we will look at the power management modes within the Cortex core. The Cortex CPU has a sleep mode that places the Core into its low power mode and halts execution of instructions within the Cortex CPU. A small part of the NVIC is kept awake, so that interrupts generated from the STM32 peripherals can wake the Cortex core up.

# 2.5.1 Entering Low Power Mode

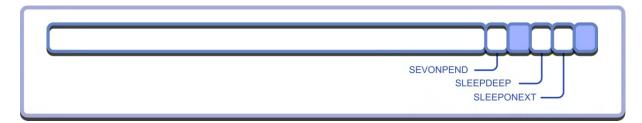

The Cortex core can be placed into its sleep mode by execution of either a Wait For Interrupt (WFI) or Wait For Event (WFE) instruction. In the case of the WFI instruction, the Cortex core will resume execution and serve the pending interrupt. Once the ISR routine has completed, there are two possibilities. Firstly, the Cortex CPU can return from the ISR and continue execution of the background code as normal. By setting the SLEEPON EXIT bit in the System Control Register, the Cortex core will automatically enter the sleep mode once the ISR has completed. This allows a low power application to be entirely interrupt-driven, so that the Cortex core will wake up, run the appropriate code and then re-enter the sleep mode with minimal code being used for power management.

The WFE interrupt allows the Cortex core to resume execution from the point it was placed into the sleep mode. It does not jump to a service routine. A wake-up event is simply a peripheral interrupt line that is not enabled as an interrupt within the NVIC. This allows a peripheral to signal the Cortex core to wake up and continue processing without the need for an interrupt service routine. The WFI and WFE instructions are not reachable from the C language, but compilers for the Thumb-2 instruction set provide intrinsic macros that can be used inline with standard C commands:

| <br>WFI |

|---------|

| WFE     |

In addition to the SLEEPNOW and SLEEPONEXIT low power modes the Cortex core can issue a SLEEPDEEP signal to the rest of the microcontroller system.

The System control register configures the Cortex processor sleep modes. The STM32 has additional low power modes that use the DeepSleep signal which is exported from the Cortex processor.

This allows additional functions such as the PLL and user peripherals to be halted, so that the STM32 can enter its lowest power modes.

# 2.5.2 CoreSight Debug Support

All of the ARM CPUs have their own on-chip debug system. The ARM7 and ARM9 CPUs have as a minimum a JTAG port which allows a standard debug tool to connect to the CPU and download code into the internal RAM or FLASH memory. The JTAG port also supports basic run control (single step and setting breakpoints etc) as well as being able to view the contents of memory locations. The ARM7 and ARM9 CPUs can also provide a real-time trace through an additional debug peripheral called the embedded trace macro cell (ETM). While this system works fine, it does have some limitations. The JTAG debug peripheral can only provide debug information to the development tools when the ARM CPU is halted, so there is no possibility of real-time updates. Also, the number of hardware breakpoints is limited to two, though the ARM7 and ARM9 instructions sets include a breakpoint

instruction which can be patched into the code by the development tool (typically called soft breakpoints.) Similarly for the real-time trace to work, the ETM must be fitted by the manufacturer at additional cost. Consequently this is not always supported. With the new Cortex core a whole new debug system called CoreSight has been introduced.

The Cortex CoreSight debug system uses a JTAG or serial wire interface. CoreSight provides run control and trace functions. It has the additional advantage that it can be kept running while the STM32 is in a low power mode. This is a big step on from standard JTAG debugging.

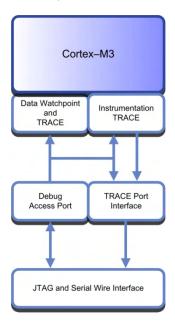

The full core sight debug system has a debug access port which allows connection to the microcontroller by a JTAG tool. The debug tool can connect using the standard 5 pin JTAG interface or a serial 2 wire interface. In addition to the JTAG debug features, the full CoreSight debug system contains a Data Watch trace and an embedded trace macro cell. For software testing there is instrumentation trace and FLASH patch block. The STM32 implements the CoreSight debug system with the omission of the embedded trace macro cell.

In practice, the CoreSight debug structure on the STM32 provides an enhanced real-time version of the standard JTAG debug features. The STM32 CoreSight debug system provides 8 hardware breakpoints which can be non-intrusively set and cleared while the Cortex CPU is running. In addition the Data Watch trace allows you to view the contents of memory locations non intrusively while the Cortex CPU is running. The CoreSight debug system can stay active when the Cortex core enters a low power or sleep mode. This makes a world of difference when debugging a low power application. Additionally the STM32 timers can be halted when the CPU is halted by the CoreSight system. This allows you to single-step your code and keep the timers in synchronisation with the instructions executing on the Cortex CPU. The CoreSight debug infrastructure significantly improves the real-time debug capabilities of the STM32 over earlier ARM7 and ARM9 CPUs whilst still using the same low cost hardware.

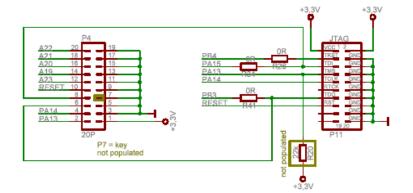

#### 2.5.2.1 Instruction Trace

The STM32 high density devices include an additional debug module called the Embedded Trace Macrocell. The ETM is designed to stream a trace of instruction execution and data read\writes. This information is streamed in a compressed format that allows an external trace tool to capture all the necessary information to reconstruct a trace of your program's execution. Like all of the CoreSight debug modules, the ETM is fully independent of the CPU and does not affect the real-time performance of the STM32. To use the ETM 7 pins must be used as additional debug pins as shown in the diagram below. The ETM pins are connected to a Samtec FSH-120, 20 pin header. This is an industry standard connector for ETM trace tools.

The High Density line devices include an internal Instruction trace unit called the Embedded Trace Macro cell. This requires an additional trace socket that should be part of your hardware design

The use of an ETM trace tool significantly increases the debug capabilities available to a developer. A bug that could take weeks to fix with just a JTAG tool and a lot of head scratching can be fixed in hours or even minutes with the information provided from a trace tool. The cost of such tools has been dropping dramatically over the last few years to the point where it is practical for every developer to have a JTAG and ETM debugger. Even if you do not currently have such a tool, you should design the ETM socket on to your hardware. Then if you do encounter a complex bug you have the option to use a trace tool.

The Embedded Trace

Macrocell and trace tool

can stream trace data to a

PC hard disk. This allows

you to extensively profile

and optimise your

application code

The ETM is not just for debugging. Because it provides timing information, the trace data can be used for software analysis such as performance analysis and code coverage. If you are developing for a safety-critical or high integrity application this kind of analysis is often a requirement.

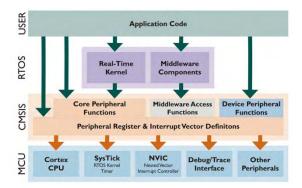

# 2.6 Cortex Microcontroller Software Interface Standard

As we have seen in the last chapter, the Cortex-M3 processor defines new levels of performance at a price point that competes with traditional 8-bit microcontrollers. The Cortex-M3 has in fact replaced the traditional classification of 8/16/32-bit microcontrollers. You can now simply select a Cortex-based microcontroller on the basis of price versus peripherals. At the time of writing, the Cortex-M3 processor has been licensed by over 20 companies. This wide adoption of Cortex-M3 has created the additional benefit of an industry-wide standard microcontroller.

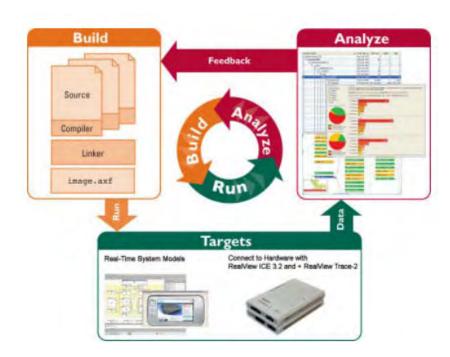

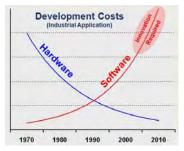

As microcontrollers have more and more sophisticated peripherals it becomes easier to design complex hardware. However, the software required to drive this generation of hardware has a matching complexity, takes longer to produce and is a rising cost.

As the hardware complexity of microcontrollers increases, the cost of hardware development is falling, in line with Moores Law. However, the complexity of software required to meet the functional specification is rising exponentially

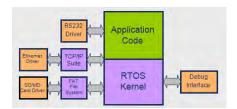

Traditionally, an embedded software developer working with a small microcontroller has always been faced with developing on the bare metal. This meant developing your own low-level drivers and rarely using an RTOS. While this was fine for a relatively simple project, it was a major barrier to code portability and reuse to say nothing of the time taken to reinvent the wheel.

The traditional software model for microcontroller development relies on custom low-level drivers often without an RTOS

Some silicon providers like ST recognise these problems and provide an open source driver library for their devices. While this gives you a headstart in code development, vendor libraries are not without their own problems. The approach taken by each vendor is different and can be hard to understand. There is often an overwhelming number of low-level functions which are quite generalised. This leads to a bloating of your code. If you are using any kind of middleware the library functions will have to be rewritten anyway.

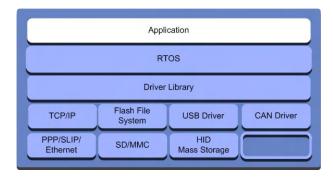

In order to meet the new design challenges a new design approach is required. Increased abstraction with a small RTOS and an industry standard driver layer - CMSIS

With this background the leading silicon vendors and tools companies have defined a new software standard called the 'Cortex Microcontroller Software Interface Standard'. CMSIS provides an industry standard driver level interface across all Cortex-based microcontrollers. The goal of CMSIS is simply to make software drivers and components as easy to exchange as hardware components. This frees up development time to concentrate on building the best application code possible.

CMSIS specifies three groups of driver functions common to all Cortex-M3 devices :

Cortex-M3 core peripheral functions

MCU device peripheral functions

Middleware access functions

The CMSIS driver layer is intended to be truly portable and will work with different vendors' compilers, RTOS and middleware. The actual CMSIS library has been deliberately kept as simple as possible. Written to the MISRA C software coding guidelines, CMSIS consists of a small number of functions providing a register level interface to the underlying microcontroller. CMSIS has three main groups of abstraction: A group of code peripheral functions to access the Cortex-M3 processor peripherals (NVIC, SYSTICK timer etc). A group of device peripheral functions to access well defined microcontroller peripherals (UART,I2C etc). Finally, more complex third party middleware such as TCP/IP stacks. USB and file systems will benefit hugely by simply accessing standard CMSIS drivers irrespective of the underlying device.

Like the Cortex-M3, the CMSIS specification creates a new era in microcontroller development. Learn the Cortex-M3 processor and CMSIS once, then apply it across a wide range of microcontrollers from many manufacturers. By providing a proven driver library, CMSIS can give you a faster route to market, It gives you code reuse, easier code maintenance and lower risk, particularly if you are using several middleware components from different vendors.

MISRA-C http://www.misra.org.uk/

CMSIS http://www.onarm.com/download/download378.asp

# 3. Getting It Working

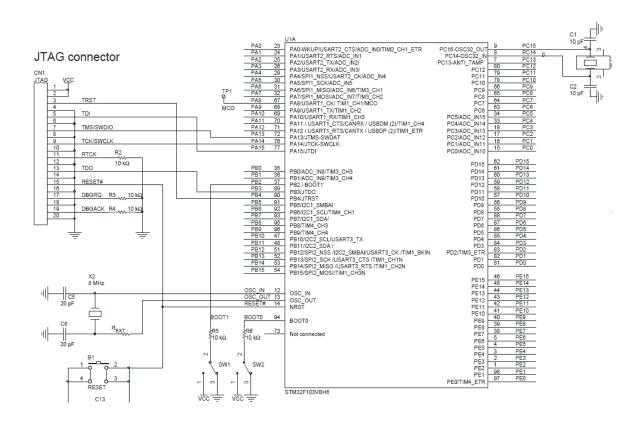

A minimal STM32 design really can be very minimal. To make the STM32 work you really just need to add a power supply. The microcontroller contains its own internal RC oscillators and an internal reset circuit. This section will look at the main hardware considerations you will need to address to build a practical design.

## 3.1 Package Types and Footprints

The STM32Performance and Access Line variants are designed with matching package types, to allow an easy hardware upgrade without any need to redesign the PCB. All the STM32 microcontrollers are available in LQFP packages ranging from 48 pins up to 144 pins.

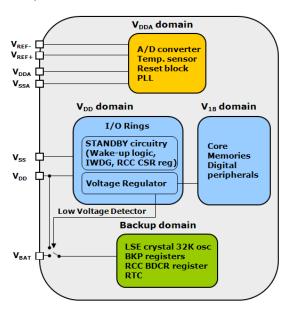

## 3.2 Power Supply

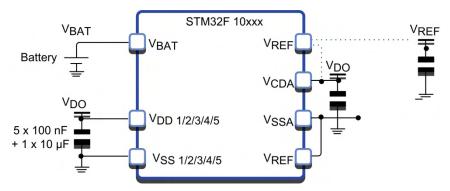

The STM32 requires a single power supply which must be in the range 2.0V to 3.6V. An internal regulator is used to generate a 1.8V supply for the Cortex core. The STM32 has two other optional power supplies. The real time clock and a small number of registers are located on a separate power domain, which can be battery-backed to preserve data when the rest of the STM32 is placed in a deep power down state. If the design is not using battery back up, then  $V_{BAT}$  must be connected to  $V_{DD}$ .

The STM32 runs from a single 2.0V-3.6V supply. There is an additional backup power domain and a separate supply for the ADC converter (144 pin package only).

The second optional power supply is used to power the ADC. If the ADC is used, the main  $V_{DD}$  power supply range is limited to 2.4V to 3.6V. On the 100 pin package, the ADC has additional voltage reference pins  $V_{REF+}$  and  $V_{REF-}$ . The  $V_{REF-}$  pin must be connected to  $V_{DDA}$  and  $V_{REF+}$  can vary from 2.4 to  $V_{DDA}$ . On all other packages the voltage reference is internally connected to the ADC voltage supply pins. Each of the power supplies requires stabilisation capacitors as shown below.

With an internal reset and an internal voltage regulator, the STM32 only needs seven external capacitors.

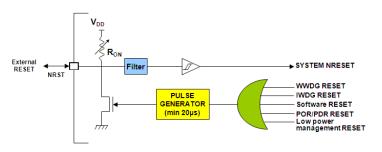

## 3.3 Reset Circuit

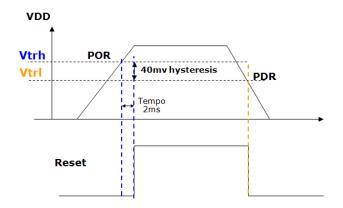

The STM32 contains an internal reset circuit that holds the device in reset as long as  $V_{DD}$  is below 2.0V with a hysteresis of 40mV.

The internal power on reset and power down reset ensure the processor only runs with a stable power supply. No external reset circuit is required.

### 3.3.1.1.1 Basic Hardware Schematic

Strictly speaking, an external reset circuit is not a necessary part of an STM32 design. However, during development the nRST pin can be connected to a simple reset switch. nRST is also routed to the JTAG debug port, so that a development tool can force a reset on the microcontroller. The STM32 has a number of internal reset sources that can detect faulty operating conditions and we will have a look at these in the safety section later on.

### 3.4 Oscillators

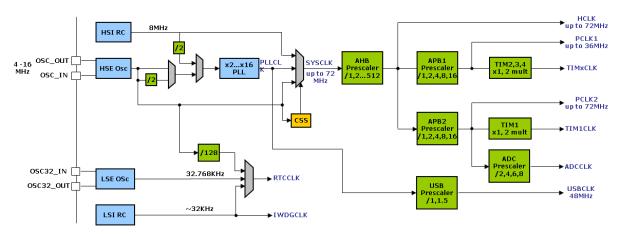

The STM32 has internal RC oscillators which are capable of supplying a clock to the internal PLL. This will allow the microcontroller to run at its maximum 72 MHz clock frequency. The internal oscillators are not as accurate or stable as an external crystal; consequently for most designs you will need at least one clock source.

## 3.4.1 High Speed External Oscillator

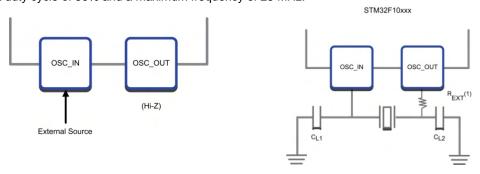

The main external clock source is used to derive the Cortex processor and the STM32 peripheral clocks. This clock source is called the High Speed External (HSE Osc) Oscillator and can be a crystal/ceramic resonator or a user provided clock source. If a user clock is selected, it can be a square, sine or triangular waveform, but it must have a duty cycle of 50% and a maximum frequency of 25 MHz.

The External Oscillator can be run from a crystal or external clock source.

If an external crystal/ceramic resonator is used, it must be in the range 4 MHz – 16 MHz. Since the internal PLL multiplies the HSE Osc frequency up by integer values, the external clock should be a factor of 72 MHz so that you can easily derive the full operating frequency.

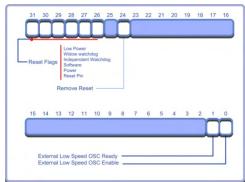

## 3.4.2 Low Speed External Oscillator

The STM32 can have a second external oscillator called the Low Speed External (LSE Osc) Oscillator. This is used to clock source to the real-time clock and the windowed watchdog.

Like the HSE Osc, the LSE Osc can be an external crystal or a user-provided clock which can again have a square, sine or triangular waveform, as long as the duty cycle is 50%. In both cases the LSE Osc should have a frequency of 32.768 KHz, as this will provide an accurate working frequency for the real-time clock. The internal low speed oscillator can be used to supply the real-time clock, but it is not highly accurate so if you plan to use the RTC to any extent in your design you should fit the LSE oscillator.

#### 3.4.3 Clock Output

One of the GPIO pins can be configured to be a Microcontroller Clock out pin. In this mode the MCO pin can output one of four internal clock sources. We will look at this in more detail when we examine the internal clock tree configuration.

### 3.4.4 Boot Pins And Field Programming

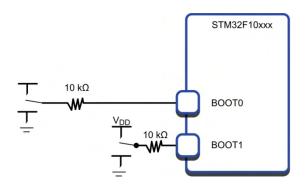

The can be started in one of three different boot modes. These modes are selected by two external boot pins BOOT0 and BOOT1. By changing the boot mode the microcontroller will alias different areas of the memory map to the bottom of memory. This allows us to execute code from user FLASH, internal SRAM or system memory. If system memory is selected, the STM32 will start to execute a factory- programmed bootloader which allows the user flash to be reprogrammed.

#### 3.4.5 Boot Modes

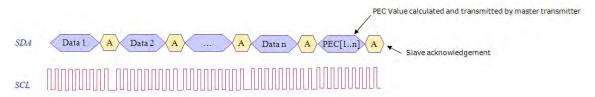

For normal operation BOOT0 must be tied to ground. If you wish to use the other modes you must provide jumpers to allow different settings on the two boot pins.

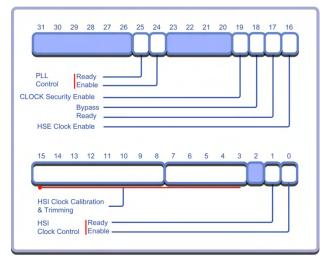

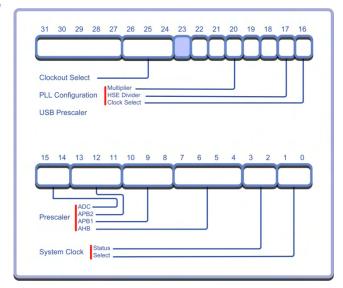

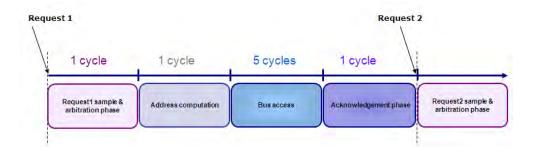

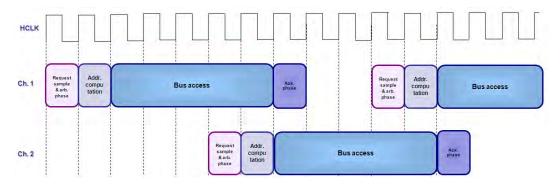

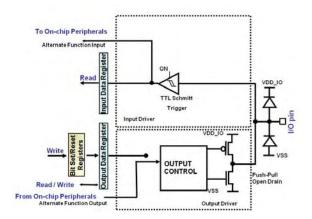

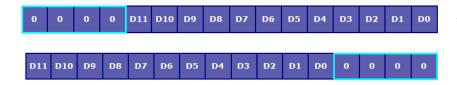

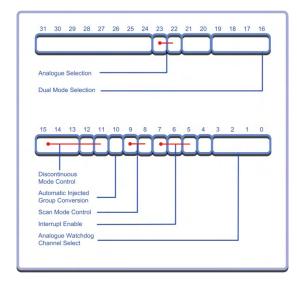

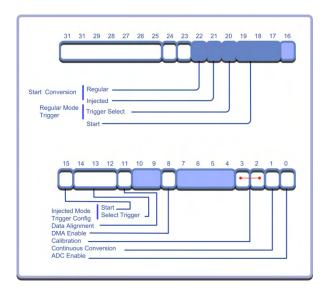

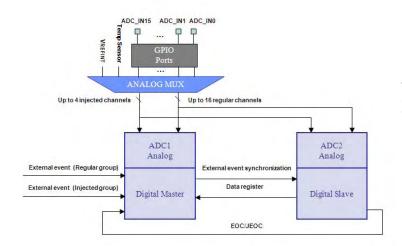

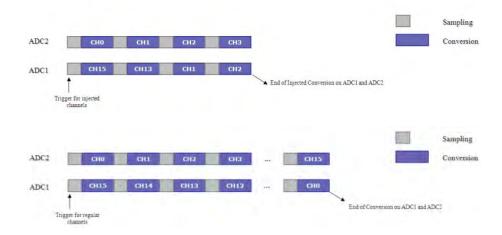

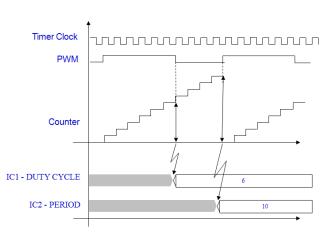

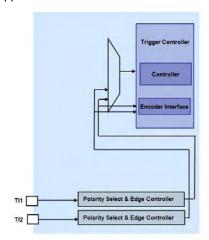

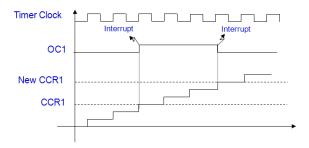

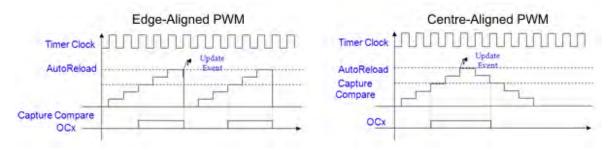

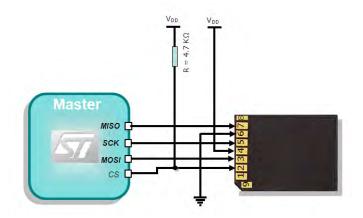

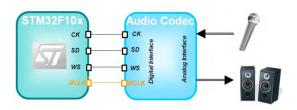

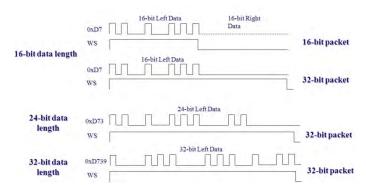

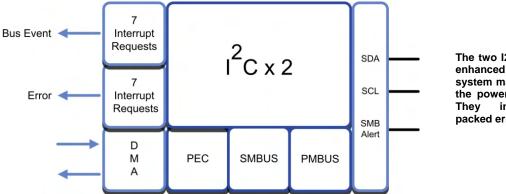

The external boot pins are used to select which region of memory aliased to the first 2k of memory. This can be user Flash, the internal bootloader or the first 2k of SRAM